Цифровые схемы - регистры сдвига

Мы знаем, что один триггер может хранить один бит информации. Чтобы хранить несколько битов информации, нам нужно несколько триггеров. Группа триггеров, которые используются для хранения (хранения) двоичных данных, известна какregister.

Если регистр может сдвигать биты в правую или левую сторону, это называется shift register. Регистр сдвига «N» битов содержит «N» триггеров. Ниже приведены четыре типа регистров сдвига, основанные на применении входов и доступе к выходам.

- Сдвиговый регистр Serial In - Serial Out

- Сдвиговый регистр Serial In - Parallel Out

- Регистр сдвига Parallel In - Serial Out

- Регистр сдвига Parallel In - Parallel Out

Регистр сдвига последовательного входа - выхода (SISO)

Регистр сдвига, который обеспечивает последовательный ввод и производит последовательный вывод, известен как Serial In - Serial Out. (SISO)регистр сдвига. Вblock diagram 3-битного регистра сдвига SISO показано на следующем рисунке.

Эта блок-схема состоит из трех D-триггеров, которые cascaded. Это означает, что выход одного D-триггера подключен как вход следующего D-триггера. Все эти триггеры синхронизированы друг с другом, поскольку на каждый из них подается один и тот же тактовый сигнал.

В этом регистре сдвига мы можем посылать биты последовательно с входа самого левого D-триггера. Следовательно, этот вход также называетсяserial input. При каждом срабатывании тактового сигнала по положительному фронту данные переходят от одной стадии к другой. Итак, мы можем получать биты последовательно с выхода самого правого D-триггера. Следовательно, этот вывод также называетсяserial output.

пример

Давайте посмотрим, как работает 3-битный регистр сдвига SISO, отправив двоичную информацию “011” последовательно от LSB к MSB на входе.

Предположим, начальный статус D-триггеров от крайнего левого до крайнего правого равен $ Q_ {2} Q_ {1} Q_ {0} = 000 $. Мы можем понятьworking of 3-bit SISO shift register из следующей таблицы.

| Нет положительного фронта часов | Последовательный вход | 2 квартал | Q 1 | Q 0 |

|---|---|---|---|---|

| 0 | - | 0 | 0 | 0 |

| 1 | 1 (младший бит) | 1 | 0 | 0 |

| 2 | 1 | 1 | 1 | 0 |

| 3 | 0 (MSB) | 0 | 1 | 1 (младший бит) |

| 4 | - | - | 0 | 1 |

| 5 | - | - | - | 0 (MSB) |

Первоначальный статус D-триггеров в отсутствие тактового сигнала равен $ Q_ {2} Q_ {1} Q_ {0} = 000 $. Здесь последовательный вывод поступает из $ Q_ {0} $. Таким образом, LSB (1) получен на 3- м положительном фронте тактового сигнала, а MSB (0) получен на 5- м положительном фронте тактового сигнала.

Следовательно, 3-битный регистр сдвига SISO требует пяти тактовых импульсов для получения действительного выхода. Точно так жеN-bit SISO shift register требует 2N-1 тактовые импульсы для сдвига N-битной информации.

Регистр сдвига последовательного входа - параллельного выхода (SIPO)

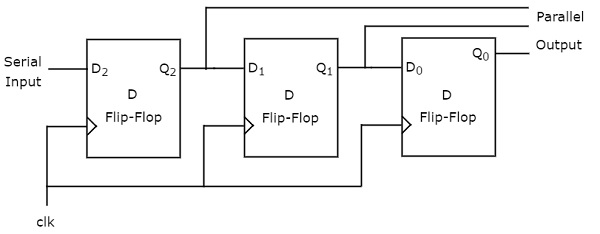

Регистр сдвига, который обеспечивает последовательный ввод и производит параллельный вывод, известен как последовательный вход - параллельный выход. (SIPO)регистр сдвига. Вblock diagram 3-битного регистра сдвига SIPO показано на следующем рисунке.

Эта схема состоит из трех каскадных D-триггеров. Это означает, что выход одного D-триггера подключен как вход следующего D-триггера. Все эти триггеры синхронизированы друг с другом, поскольку на каждый из них подается один и тот же тактовый сигнал.

В этом регистре сдвига мы можем посылать биты последовательно с входа самого левого D-триггера. Следовательно, этот вход также называетсяserial input. При каждом срабатывании тактового сигнала по положительному фронту данные переходят от одной стадии к другой. В этом случае мы можем получить доступ к выходам каждого D-триггера параллельно. Итак, мы получимparallel outputs из этого регистра сдвига.

пример

Давайте посмотрим, как работает 3-битный регистр сдвига SIPO, отправив двоичную информацию “011” последовательно от LSB к MSB на входе.

Предположим, начальный статус D-триггеров от крайнего левого до крайнего правого равен $ Q_ {2} Q_ {1} Q_ {0} = 000 $. Здесь $ Q_ {2} $ и $ Q_ {0} $ - это старший и младший бит соответственно. Мы можем понятьworking of 3-bit SIPO shift register из следующей таблицы.

| Нет положительного фронта часов | Последовательный вход | Q 2 (MSB) | Q 1 | Q 0 (младший бит) |

|---|---|---|---|---|

| 0 | - | 0 | 0 | 0 |

| 1 | 1 (младший бит) | 1 | 0 | 0 |

| 2 | 1 | 1 | 1 | 0 |

| 3 | 0 (MSB) | 0 | 1 | 1 |

Первоначальный статус D-триггеров в отсутствие тактового сигнала равен $ Q_ {2} Q_ {1} Q_ {0} = 000 $. Бинарная информация“011” получается параллельно на выходах D триггеров для третьего положительного фронта тактового сигнала.

Таким образом, 3-битный регистр сдвига SIPO требует трех тактовых импульсов для получения действительного вывода. Точно так жеN-bit SIPO shift register требует N тактовые импульсы для сдвига N-битной информации.

Регистр сдвига параллельного входа - последовательного выхода (PISO)

Регистр сдвига, который позволяет параллельный ввод и производит последовательный вывод, известен как параллельный вход - последовательный выход. (PISO)регистр сдвига. Вblock diagram 3-битного сдвигового регистра PISO показано на следующем рисунке.

Эта схема состоит из трех каскадных D-триггеров. Это означает, что выход одного D-триггера подключен как вход следующего D-триггера. Все эти триггеры синхронизированы друг с другом, поскольку на каждый из них подается один и тот же тактовый сигнал.

В этом регистре сдвига мы можем применить parallel inputsдля каждого D-триггера, установив для параметра Preset Enable значение 1. При каждом срабатывании положительного фронта синхросигнала данные переходят от одного этапа к другому. Итак, мы получимserial output от правого самого D триггера.

пример

Давайте посмотрим на работу 3-битного сдвигового регистра PISO, применив двоичную информацию “011” параллельно через предустановленные входы.

Поскольку предустановленные входные параметры применяются до положительного фронта тактового сигнала, начальное состояние D-триггеров от крайнего левого до крайнего правого будет $ Q_ {2} Q_ {1} Q_ {0} = 011 $. Мы можем понятьworking of 3-bit PISO shift register из следующей таблицы.

| Нет положительного фронта часов | 2 квартал | Q 1 | Q 0 |

|---|---|---|---|

| 0 | 0 | 1 | 1 (младший бит) |

| 1 | - | 0 | 1 |

| 2 | - | - | 0 (младший бит) |

Здесь последовательный вывод поступает из $ Q_ {0} $. Таким образом, LSB (1) получен до применения положительного фронта тактового сигнала, а MSB (0) получен на 2- м положительном фронте тактового сигнала.

Следовательно, 3-битный сдвиговый регистр PISO требует двух тактовых импульсов для получения действительного выхода. Точно так жеN-bit PISO shift register требует N-1 тактовые импульсы для сдвига N-битной информации.

Регистр сдвига с параллельным входом - параллельным выходом (PIPO)

Регистр сдвига, который обеспечивает параллельный ввод и производит параллельный вывод, известен как параллельный ввод - параллельный вывод. (PIPO)регистр сдвига. Вblock diagram 3-битного сдвигового регистра PIPO показано на следующем рисунке.

Эта схема состоит из трех каскадных D-триггеров. Это означает, что выход одного D-триггера подключен как вход следующего D-триггера. Все эти триггеры синхронизированы друг с другом, поскольку на каждый из них подается один и тот же тактовый сигнал.

В этом регистре сдвига мы можем применить parallel inputsдля каждого D-триггера, установив для параметра Preset Enable значение 1. Мы можем применить параллельные входы через preset или clear. Это два асинхронных входа. Это означает, что триггеры производят соответствующие выходные данные на основе значений асинхронных входов. В этом случае влияние выходов не зависит от тактового перехода. Итак, мы получимparallel outputs от каждого D-триггера.

пример

Давайте посмотрим на работу 3-битного сдвигового регистра PIPO, применив двоичную информацию “011” параллельно через предустановленные входы.

Поскольку предустановленные входные параметры применяются до положительного фронта тактового сигнала, начальное состояние D-триггеров от крайнего левого до крайнего правого будет $ Q_ {2} Q_ {1} Q_ {0} = 011 $. Итак, двоичная информация“011” получается параллельно на выходах D-триггеров до подачи положительного фронта тактового сигнала.

Следовательно, 3-битный сдвиговый регистр PIPO требует нулевых тактовых импульсов для получения действительного выхода. Точно так жеN-bit PIPO shift register не требует никаких тактовых импульсов для смещения информации «N» битов.